1. Overview

The NEORV32 RISC-V Processor is an open-source RISC-V compatible processor system that is intended as ready-to-go auxiliary processor within a larger SoC designs or as stand-alone custom / customizable microcontroller.

The system is highly configurable and provides optional common peripherals like embedded memories, timers, serial interfaces, general purpose IO ports and an external bus interface to connect custom IP like memories, NoCs and other peripherals. On-line and in-system debugging is supported by an OpenOCD/gdb compatible on-chip debugger accessible via JTAG.

Special focus is paid on execution safety to provide defined and predictable behavior at any time. Therefore, the CPU ensures that all memory access are acknowledged and no invalid/malformed instructions are executed. Whenever an unexpected situation occurs, the application code is informed via hardware exceptions.

The software framework of the processor comes with application makefiles, software libraries for all CPU and processor features, a bootloader, a runtime environment and several example programs - including a port of the CoreMark MCU benchmark and the official RISC-V architecture test suite. RISC-V GCC is used as default toolchain.

Check out the processor’s online User Guide that provides hands-on tutorials to get you started.

Structure

1.1. Project Key Features

Project

-

all-in-one package: CPU + SoC + Software Framework & Tooling

-

completely described in behavioral, platform-independent VHDL - no vendor- or technology-specific primitives, attributes, macros, libraries, etc. are used at all

-

all-Verilog "version" available (auto-generated by GHDL)

-

extensive configuration options for adapting the processor to the requirements of the application

-

highly extensible hardware - on CPU, SoC and system level

-

aims to be as small as possible while being as RISC-V-compliant as possible - with a reasonable area-vs-performance trade-off

-

FPGA friendly (e.g. all internal memories can be mapped to block RAM - including the register file)

-

optimized for high clock frequencies to ease timing closure and integration

-

from zero to "hello world!" - completely open source and documented

-

easy to use even for FPGA/RISC-V starters – intended to work out of the box

NEORV32 CPU (the core)

-

32-bit RISC-V CPU

-

fully compatible to the RISC-V ISA specs. - checked by the official RISC-V architecture compatibility tests

-

base ISA + privileged ISA + several optional standard and custom ISA extensions

-

option to add user-defined RISC-V instructions as custom ISA extension

-

rich set of customization options (ISA extensions, design goal: performance / area / energy, tuning options, …)

-

Full Virtualization capabilities to increase execution safety

-

official RISC-V open source architecture ID

NEORV32 Processor (the SoC)

-

highly-configurable full-scale microcontroller-like processor system

-

based on the NEORV32 CPU

-

optional standard serial interfaces (UART, TWI, SPI (host and device), 1-Wire)

-

optional timers and counters (watchdog, system timer)

-

optional general purpose IO and PWM; a native NeoPixel(c)-compatible smart LED interface

-

optional embedded memories and caches for data, instructions and bootloader

-

optional external memory interface for custom connectivity

-

optional DMA controller for CPU-independent data transfers

-

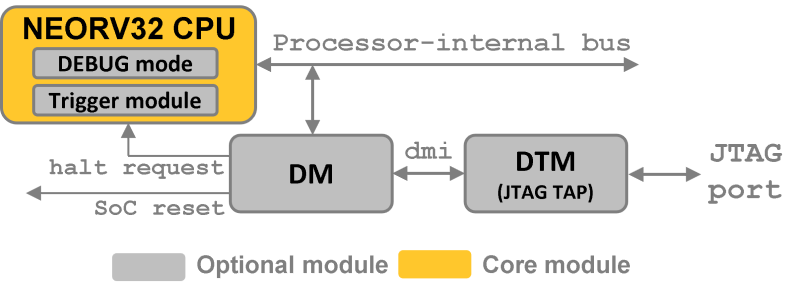

on-chip debugger compatible with OpenOCD and GDB including hardware trigger module and optional authentication

Software framework

-

written in C and based on GCC

-

internal bootloader with serial user interface (via UART)

-

core libraries and HAL for high-level usage of the provided functions and peripherals

-

processor-specific runtime environment and several example programs

-

Doxygen-based documentation of the software framework; a deployed version is available at https://stnolting.github.io/neorv32/sw/files.html

-

Ada support at https://github.com/GNAT-Academic-Program/neorv32-hal

OS Support

-

FreeRTOS port: https://github.com/stnolting/neorv32-freertos

-

Upstream Zephyr support: https://docs.zephyrproject.org/latest/boards/others/neorv32/doc/index.html

-

MicroPython port: https://github.com/stnolting/neorv32-micropython

Extensibility and Customization

The NEORV32 processor is designed to ease customization and extensibility and provides several options for adding application-specific custom hardware modules and accelerators. The three most common options for adding custom on-chip modules are listed below.

-

Processor-External Bus Interface (XBUS) to attach processor-external IP modules (memories and peripherals)

-

Custom Functions Subsystem (CFS) for tightly-coupled processor-internal co-processors

-

Custom Functions Unit (CFU) for custom RISC-V instructions

| A more detailed comparison of the extension/customization options can be found in section Adding Custom Hardware Modules of the user guide. |

1.2. Project Folder Structure

The root directory of the repository is considered the NEORV32 base or home folder (i.e. neorv32/).

neorv32 - Project home folder │ ├─ docs - Documentation │ ├─ datasheet - AsciiDoc sources for the NEORV32 data sheet │ ├─ figures - Figures and logos │ ├─ references - Data sheets and RISC-V specs │ └─ userguide - AsciiDoc sources for the NEORV32 user guide │ ├─ rtl - HDL sources │ ├─ core - Core sources of the CPU & SoC │ ├─ system_integration - System wrappers and bridges for advanced SoC connectivity │ ├─ test_setups - Minimal test setup "SoCs" used in the User Guide │ └─ verilog - Scripts and examples for converting NEORV32 to Verilog │ ├─ sim - Simulation files │ └─ sw - Software framework ├─ bootloader - Sources of the default builtin bootloader ├─ common - Linker script, crt0.S start-up code and central makefile ├─ example - Example programs for the core and the SoC modules │ ├─ eclipse - Pre-configured Eclipse IDE project │ └─ ... - Several example programs ├─ image_gen - Helper program to generate executables & memory images ├─ lib - NEORV32 core library ├─ ocd_firmware - Firmware for the on-chip debugger "park loop" ├─ openocd - OpenOCD configuration files └─ svd - Processor system view description file (CMSIS-SVD)

1.3. VHDL File Hierarchy

All required VHDL hardware source files are located in the project’s rtl/core folder.

|

VHDL Library

All core VHDL files from the list below have to be assigned to a new library named neorv32.

|

|

Compilation Order

See section File-List Files for more information.

|

|

Replacing Modules for Customization or Optimization (Especially Memory Modules)

Any module of the core can be replaced for customization purpose.

For ASIC implementations (and for some FPGA implementations), this is particularly recommended for

the underlying memories. Therefore, all (larger) memories are encapsulated as easily replaceable IP

wrappers (i.e. *_ram.vhd and *_rom.vhd files). By default, these wrappers use a generic memory

description that should infer blockRAM on most FPGA platforms.

|

rtl/core │ ├─ neorv32_bootrom.vhd - Bootloader ROM ├─ neorv32_bootrom_image.vhd - Bootloader ROM initialization image ├─ neorv32_bootrom_rom.vhd - Bootloader ROM primitive wrapper ├─ neorv32_bus.vhd - SoC bus infrastructure modules ├─ neorv32_cache.vhd - Generic cache module ├─ neorv32_cache_ram.vhd - Cache tag and data RAM primitive wrapper ├─ neorv32_cfs.vhd - Custom functions subsystem ├─ neorv32_clint.vhd - Core local interruptor ├─ neorv32_cpu.vhd - NEORV32 CPU TOP ENTITY ├─ neorv32_cpu_alu.vhd - Arithmetic/logic unit ├─ neorv32_cpu_control.vhd - CPU control, exception system and CSRs ├─ neorv32_cpu_counters.vhd - Hardware counters (Zicntr & Zihpm ext.) ├─ neorv32_cpu_alu_bitmanip.vhd - Bit-manipulation unit (B ext.) ├─ neorv32_cpu_alu_cfu.vhd - Custom instructions unit (Xcfu ext.) ├─ neorv32_cpu_alu_cond.vhd - Integer conditional unit (Zicond ext.) ├─ neorv32_cpu_alu_crypto.vhd - Scalar cryptography unit (Zk*/Zbk* ext.) ├─ neorv32_cpu_alu_fpu.vhd - Floating-point unit (Zfinx ext.) ├─ neorv32_cpu_alu_muldiv.vhd - Integer MUL/DIV unit (M ext.) ├─ neorv32_cpu_alu_shifter.vhd - Bit-shift unit (base ISA) ├─ neorv32_cpu_decompressor.vhd - Compressed instructions decoder (C ext.) ├─ neorv32_cpu_frontend.vhd - Instruction fetch and issue ├─ neorv32_cpu_hwtrig.vhd - Hardware trigger module (Sdtrig ext.) ├─ neorv32_cpu_lsu.vhd - Load/store unit ├─ neorv32_cpu_pmp.vhd - Physical memory protection unit (Smpmp ext.) ├─ neorv32_cpu_regfile.vhd - Data register file ├─ neorv32_cpu_trace.vhd - Trace generator ├─ neorv32_debug_auth.vhd - On-chip debugger: authentication module ├─ neorv32_debug_dm.vhd - On-chip debugger: debug module ├─ neorv32_debug_dtm.vhd - On-chip debugger: debug transfer module ├─ neorv32_dma.vhd - Direct memory access controller ├─ neorv32_dmem.vhd - Data memory ├─ neorv32_dmem_ram.vhd - Data memory RAM primitive wrapper ├─ neorv32_gpio.vhd - General purpose input/output port unit ├─ neorv32_gptmr.vhd - General purpose 32-bit timer ├─ neorv32_imem.vhd - Instruction memory ├─ neorv32_imem_image.vhd - Instruction memory initialization image ├─ neorv32_imem_ram.vhd - Instruction memory RAM primitive wrapper ├─ neorv32_imem_rom.vhd - Instruction memory ROM primitive wrapper ├─ neorv32_neoled.vhd - NeoPixel (TM) compatible smart LED interface ├─ neorv32_onewire.vhd - One-Wire serial interface controller ├─ neorv32_package.vhd - Main VHDL package file ├─ neorv32_prim.vhd - Generic RTL primitives ├─ neorv32_pwm.vhd - Pulse-width modulation controller ├─ neorv32_sdi.vhd - Serial data interface controller (SPI device) ├─ neorv32_slink.vhd - Stream link interface ├─ neorv32_spi.vhd - Serial peripheral interface controller (SPI host) ├─ neorv32_sys.vhd - System infrastructure modules ├─ neorv32_sysinfo.vhd - System configuration information memory ├─ neorv32_top.vhd - NEORV32 PROCESSOR/SOC TOP ENTITY ├─ neorv32_tracer.vhd - Instruction trace buffer ├─ neorv32_trng.vhd - True random number generator ├─ neorv32_twd.vhd - Two wire serial device controller ├─ neorv32_twi.vhd - Two wire serial interface controller ├─ neorv32_uart.vhd - Universal async. receiver/transmitter ├─ neorv32_wdt.vhd - Watchdog timer └─ neorv32_xbus.vhd - External bus interface gateway

1.3.1. File-List Files

Most of the RTL sources use entity instantiation. Hence, the RTL compile order might be relevant (depending on

the synthesis/simulation tool. Therefore, two file-list files are provided in the rtl folder that list all required

HDL files for the CPU core and for the entire processor and also represent their recommended compile order. Note that

these files list the architecture "bottom-up" - the according top entity is listed in the very last line.

These file-list files can be consumed by EDA tools to simplify project setup.

-

file_list_cpu.f- HDL files and compile order for the CPU core; top module:neorv32_cpu -

file_list_soc.f- HDL files and compile order for the entire processor/SoC; top module:neorv32_top

A simple bash script generate_file_lists.sh is provided for regenerating the file-lists (using GHDL’s elaborate command).

This script can also be invoked using the default application makefile (see Makefile Targets).

By default, the file-list files include a placeholder in the path of each included hardware source file. These placeholders need to be replaced by the actual path before being used. Example:

-

default:

NEORV32_RTL_PATH_PLACEHOLDER/core/neorv32_package.vhd -

adjusted:

path/to/neorv32/rtl/core/neorv32_package.vhd

NEORV32_HOME = path/to/neorv32 (1)

NEORV32_SOC_FILE = $(shell cat $(NEORV32_HOME)/rtl/file_list_soc.f) (2)

NEORV32_SOC_SRCS = $(subst NEORV32_RTL_PATH_PLACEHOLDER, $(NEORV32_HOME)/rtl, $(NEORV32_SOC_FILE)) (3)| 1 | Path to the NEORV32 home folder (i.e. the root folder of the GitHub repository). |

| 2 | Load the content of the file_list_soc.f file-list into a new variable NEORV32_SOC_FILE. |

| 3 | Substitute the file-list file’s path placeholder “NEORV32_RTL_PATH_PLACEHOLDER” by the actual path. |

set file_list_file [read [open "$neorv32_home/rtl/file_list_soc.f" r]]

set file_list [string map [list "NEORV32_RTL_PATH_PLACEHOLDER" "$neorv32_home/rtl"] $file_list_file]

puts "NEORV32 source files:"

puts $file_list1.4. VHDL Coding Style

-

The entire processor, including the CPU core, is written in platform-/technology-independent VHDL. The code makes minimal use of VHDL 2008 features in order to remain compatible with older EDA tools.

-

A specific VHDL library

neorv32is used for all sources. -

All registers / flip-flops provide an asynchronous reset (see Processor Reset).

-

The entire setup uses a single clock domain. External "clock" signals are synchronized into this clock domain using 2-stage shift registers.

-

A single package/library file (

neorv32_package.vhd) is used to provide global definitions and auxiliary functions. The user-defined configuration is done entirely via the generics of the top entity. -

Internally, all generics are checked to ensure correct configuration. Asserts are used to inform the user about the actual processor configuration and possible invalid settings.

-

The code uses entity instantiation for all internal modules. However, if multiple submodules are specified within the same source file, component instantiation is used for them. * When instantiating the top-level processor module (

neorv32_top.vhd) in a user-defined design, either entity instantiation or component instantiation can be used, as the NEORV32 package file/library file already provides a corresponding component declaration. -

Larger memories (IMEM, DMEM, caches) are implemented as encapsulated wrappers, which are instantiated by component instantiation. The interfaces of these blocks are static (fixed signal widths; not dependent on the configuration). This means they can be easily replaced by corresponding Verilog IP wrappers (also via black-box instantiation and late binding).

|

All-Verilog Setup

Scripts and instructions for an automatic to-Verilog conversion as well as an all-Verilog

setup that uses custom Verilog memory IPs can be found in rtl/verilog. See

UG: NEORV32 in Verilogfor more information.

|

1.5. Performance

Area Utilization

The NEORV32 processor is optimized for minimal size. However, the actual size (silicon area or FPGA resources)

depends on the specific configuration. For example, an RTOS-capable setup based on a rv32imc_Zicsr_Zicntr CPU

configuration including peripheral and memories requires about 2300 LUTs and 1000 FFs and can run at up to 130 MHz

(implementation results for an Altera Cyclone IV E EP4CE22F17C6 FPGA).

|

NEORV32 Setups

The processor has been successfully ported to AMD, Altera, Lattice, Microchip, Gowin, Cologne Chip

and NanoXplore FPGAs. Some pre-configured example setup are available online: https://github.com/stnolting/neorv32-setups

|

Processing Speed

The computational performance of the NEORV32 is evaluated using Core Mark CPU benchmark.

The according sources can be found in the sw/example/coremark folder.

| CPU | CoreMark Score | CoreMarks/MHz | Average CPI |

|---|---|---|---|

small ( |

33.89 |

0.3389 |

4.04 |

medium ( |

62.50 |

0.6250 |

5.34 |

performance ( |

95.23 |

0.9523 |

3.54 |

Performance can be further improved by enabling additional ISA extensions. Note that the compiler

also needs to support these extensions (make sure to use a multilib GCC configuration for optimal

code results).

The NEORV32 CPU is based on a multi-cycle architecture. Each instruction is executed in a sequence of several consecutive micro operations. The average CPI (cycles per instruction) depends on the instruction mix of a specific applications and also on the available CPU extensions, tuning options and memory latency.

1.6. RISC-V Compatibility

The NEORV32 CPU passes the official RISC-V Architectural Certification Tests (ACTs) to certifying it faithfully implements the RISC-V specification. The NEORV32 port of this test framework is available at https://github.com/stnolting/neorv32-riscv-act.

|

Unsupported ISA Extensions

Executing instructions or accessing CSRs from unsupported ISA extensions will raise a precise illegal

instruction exception allowing full software emulation (see section Full Virtualization).

|

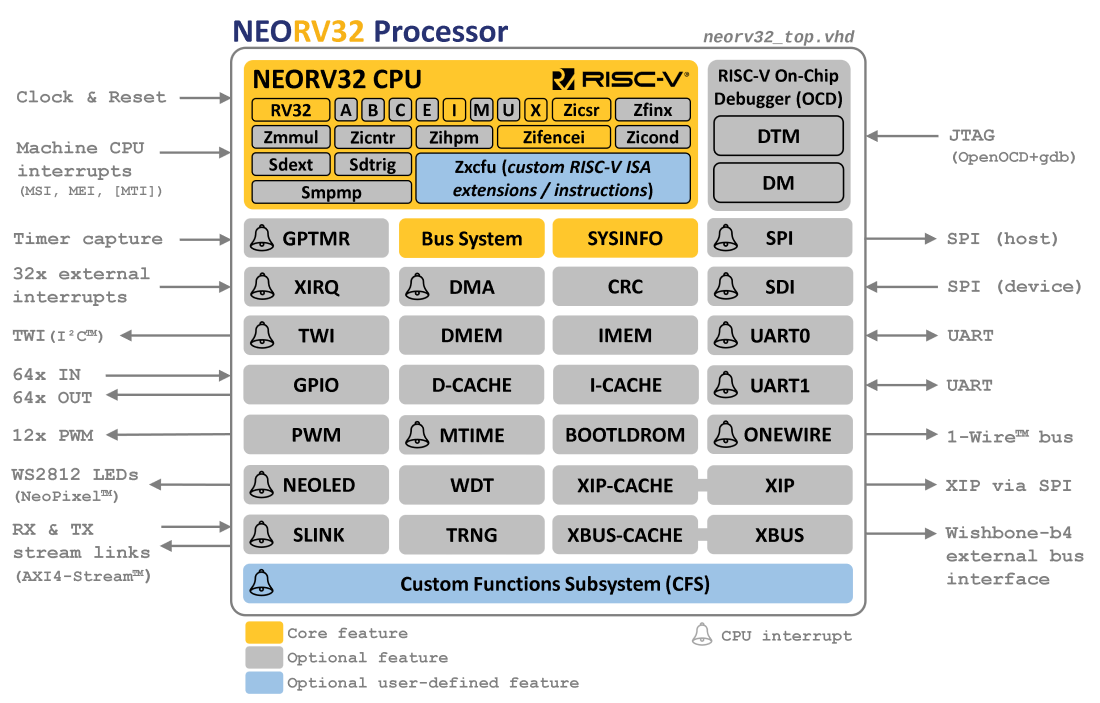

2. NEORV32 Processor (SoC)

The NEORV32 Processor provides a RISC-V-based full-scale microcontroller-like SoC platform build around the NEORV32 Central Processing Unit (CPU).

Section Structure

Key Features

-

optional SMP Dual-Core Configuration

-

optional internal bootloader (BOOTROM) with UART console & SPI/TWI flash and SD card boot options

-

optional RISC-V-compatible core local interruptor (CLINT)

-

optional two independent universal asynchronous receivers and transmitters (UART0, UART1) with optional hardware flow control (RTS/CTS)

-

optional serial peripheral interface host controller (SPI) with 8 dedicated CS lines

-

optional 8-bit serial data device interface (SDI)

-

optional two-wire serial interface controller (TWI), compatible to the I²C standard

-

optional two-wire serial device controller (TWD), compatible to the I²C standard

-

optional general purpose parallel IO port (GPIO), 32 inputs (interrupt capable), 32 outputs

-

optional 32-bit external bus interface, Wishbone-compatible (XBUS), AXI4-compatible bridge available

-

optional watchdog timer (WDT)

-

optional PWM controller with up to 32 individual channels (PWM)

-

optional ring-oscillator-based true random number generator (TRNG)

-

optional NeoPixel™/WS2812-compatible smart LED interface (NEOLED)

-

optional custom functions subsystem for custom co-processor extensions (CFS)

-

optional general purpose 32-bit timer (GPTMR) with up to 16 individual timer slices

-

optional 1-wire serial interface controller (ONEWIRE), compatible to the 1-wire standard

-

optional autonomous direct memory access controller (DMA)

-

optional stream link interface (SLINK), AXI4-Stream-compatible

-

optional on-chip debugger with JTAG TAP (OCD), optional authentication and hardware breakpoint

-

optional execution trace buffer to debug program flow (TRACER) via branch tracing

-

optional RVFI-compatible Execution Trace Port for advanced debugging, profiling and verification

-

optional system configuration information memory to determine hardware configuration via software (SYSINFO)

2.1. Processor Top Entity - Signals

The following table shows the interface signals of the processor top entity (rtl/core/neorv32_top.vhd).

All signals are of type std_ulogic or std_ulogic_vector, respectively. Custom interface type are used only

for the Execution Trace Port (trace_*).

|

Default Values of Inputs

All input signals - except for clock and reset - provide default values in case they are not explicitly assigned

during instantiation. The weak driver strengths of VHDL ('L' and 'H') are used to model a pull-down or pull-up

resistor for these unconnected inputs. After synthesis, these will result in 0 or 1, respectively.

|

|

Variable-Sized Ports

Some peripherals allow to configure the number of channels to-be-implemented by a generic (for example the number

of PWM channels). The according input/output signals have a fixed sized regardless of the actually configured

amount of channels. If less than the maximum number of channels is configured, only the LSB-aligned channels are used:

in case of an input port the remaining bits/channels are left unconnected; in case of an output port the remaining

bits/channels are hardwired to zero.

|

|

Tri-State Interfaces

Some interfaces (like the TWI, the TWD and the 1-Wire bus) require explicit tri-state drivers in the final top module.

|

|

Input/Output Registers

By default all output signals are driven by register and all input signals are synchronized into the processor’s

clock domain also using registers. However, for ASIC implementations it is recommended to add another register state

to all inputs and output so the synthesis tool can insert an explicit IO (boundary) scan chain.

|

| Name | Width | Direction | Default | Description |

|---|---|---|---|---|

Global Control (Processor Clocking and Processor Reset) |

||||

|

1 |

in |

none |

global clock line, all registers triggering on rising edge |

|

1 |

in |

none |

global reset, asynchronous, low-active |

|

1 |

out |

- |

On-Chip Debugger (OCD) reset output, synchronous, low-active |

|

1 |

out |

- |

Watchdog Timer (WDT) reset output, synchronous, low-active |

|

* |

out |

- |

CPU core 0 trace port (type |

|

* |

out |

- |

CPU core 1 trace port (type |

JTAG Access Port for On-Chip Debugger (OCD) |

||||

|

1 |

in |

|

serial clock |

|

1 |

in |

|

serial data input |

|

1 |

out |

- |

serial data output |

|

1 |

in |

|

mode select |

|

32 |

out |

- |

destination address |

|

32 |

out |

- |

read data |

|

3 |

out |

- |

cycle type |

|

3 |

out |

- |

access tag |

|

1 |

out |

- |

write enable ('0' = read transfer) |

|

4 |

out |

- |

byte enable |

|

1 |

out |

- |

strobe |

|

1 |

out |

- |

valid cycle |

|

32 |

in |

|

write data |

|

1 |

in |

|

transfer acknowledge |

|

1 |

in |

|

transfer error |

|

32 |

in |

|

RX data |

|

4 |

in |

|

RX source routing information |

|

1 |

in |

|

RX data valid |

|

1 |

in |

|

RX last element of stream |

|

1 |

out |

- |

RX ready to receive |

|

32 |

out |

- |

TX data |

|

4 |

out |

- |

TX destination routing information |

|

1 |

out |

- |

TX data valid |

|

1 |

out |

- |

TX last element of stream |

|

1 |

in |

|

TX allowed to send |

|

32 |

out |

- |

general purpose port direction control ( |

|

32 |

out |

- |

general purpose parallel output port |

|

32 |

in |

|

general purpose parallel input port (interrupt-capable) |

Primary Universal Asynchronous Receiver and Transmitter (UART0) |

||||

|

1 |

out |

- |

serial transmitter |

|

1 |

in |

|

serial receiver |

|

1 |

out |

- |

RX ready to receive new char |

|

1 |

in |

|

TX allowed to start sending, low-active |

Secondary Universal Asynchronous Receiver and Transmitter (UART1) |

||||

|

1 |

out |

- |

serial transmitter |

|

1 |

in |

|

serial receiver |

|

1 |

out |

- |

RX ready to receive new char |

|

1 |

in |

|

TX allowed to start sending, low-active |

|

1 |

out |

- |

controller clock line |

|

1 |

out |

- |

serial data output |

|

1 |

in |

|

serial data input |

|

8 |

out |

- |

select (low-active) |

|

1 |

in |

|

controller clock line |

|

1 |

out |

- |

serial data output |

|

1 |

in |

|

serial data input |

|

1 |

in |

|

chip select, low-active |

|

1 |

in |

|

serial data line sense input |

|

1 |

out |

- |

serial data line output (pull low only) |

|

1 |

in |

|

serial clock line sense input |

|

1 |

out |

- |

serial clock line output (pull low only) |

|

1 |

in |

|

serial data line sense input |

|

1 |

out |

- |

serial data line output (pull low only) |

|

1 |

in |

|

serial clock line sense input |

|

1 |

in |

|

1-wire bus sense input |

|

1 |

out |

- |

1-wire bus output (pull low only) |

|

16 |

out |

- |

pulse-width modulated channels |

|

256 |

in |

|

custom CFS input signal conduit |

|

256 |

out |

- |

custom CFS output signal conduit |

|

1 |

out |

- |

asynchronous serial data output |

|

64 |

out |

- |

CLINT.MTIMER system time output |

RISC-V Machine-Mode Processor Interrupts |

||||

|

1 |

in |

|

machine software interrupt (RISC-V), high-level-active; available only if CLINT is not enabled |

|

1 |

in |

|

machine timer interrupt (RISC-V), high-level-active; available only if CLINT is not enabled |

|

1 |

in |

|

machine external interrupt (RISC-V), high-level-active |

2.2. Processor Top Entity - Generics

This section lists all configuration generics of the NEORV32 processor top entity (rtl/neorv32_top.vhd).

These generics allow to configure the system according to your needs. The generics are

used to control implementation of certain CPU extensions and peripheral modules and even allow to

optimize the system for certain design goals like minimal area or maximum performance.

|

Default Values

All configuration generics provide default values in case they are not explicitly assigned during instantiation.

By default, all configuration options are disabled.

|

|

Software Discovery of Configuration

Software can determine the actual CPU configuration via the misa and mxisa[h] CSRs. The SoC/Processor configuration

can be determined via the SYSINFO memory-mapped registers.

|

| Name | Type | Default | Description |

|---|---|---|---|

General |

|||

|

natural |

0 |

The clock frequency of the processor’s |

|

boolean |

false |

Enable external CPU execution Execution Trace Port. |

|

boolean |

false |

Enable the SMP Dual-Core Configuration. |

|

natural |

0 |

Boot mode select; see Boot Configuration. |

|

suv(31:0) |

x"00000000" |

Custom CPU boot address (available if |

|

boolean |

false |

Implement the on-chip debugger and the CPU debug mode ( |

|

natural |

0 |

Number of implemented HW triggers (Trigger Module / |

|

boolean |

false |

Implement Debug Authentication module. |

|

suv(10:0) |

"00000000000" |

JEDEC ID: continuation codes plus vendor ID. |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable |

|

boolean |

false |

Enable NEORV32-specific |

|

boolean |

false |

Implement constant-time branches (same execution times for taken and not-taken branches). |

|

boolean |

false |

Implement fast but large full-parallel multipliers (trying to infer DSP blocks); see section CPU Arithmetic Logic Unit. |

|

boolean |

false |

Implement fast but large full-parallel barrel shifters; see section CPU Arithmetic Logic Unit. |

|

natural |

0 |

CPU register file implementation style select; see section CPU Register File. |

Physical Memory Protection ( |

|||

|

natural |

0 |

Number of implemented PMP regions (0..16). |

|

natural |

4 |

Minimal region granularity in bytes. Has to be a power of two, min 4. |

|

boolean |

false |

Implement support for top-of-region (TOR) mode. |

|

boolean |

false |

Implement support for naturally-aligned power-of-two (NAPOT & NA4) modes. |

Hardware Performance Monitors ( |

|||

|

natural |

0 |

Number of implemented hardware performance monitor counters (0..29). |

|

natural |

64 |

Total LSB-aligned size of each HPM counter. Min 0, max 64. |

Internal Instruction Memory (IMEM) |

|||

|

boolean |

false |

Implement instruction memory. |

|

suv(31:0) |

x"00000000" |

Base address of the instruction memory (has to be naturally-aligned to its size). Handle with care. |

|

natural |

16*1024 |

Size in bytes of the instruction memory (use a power of 2). |

|

boolean |

false |

Add IMEM output register stage (improves mapping/timing at the expense of latency). |

Internal Data Memory (DMEM) |

|||

|

boolean |

false |

Implement data memory. |

|

suv(31:0) |

x"80000000" |

Base address of the data memory (has to be naturally-aligned to its size). Handle with care. |

|

natural |

8*1024 |

Size in bytes of the data memory (use a power of 2). |

|

boolean |

false |

Add DMEM output register stage (improves mapping/timing at the expense of latency). |

CPU Caches (Instruction Cache (iCache) & Data Cache (dCache)) |

|||

|

boolean |

false |

Implement the instruction cache ("I$"). |

|

natural |

4 |

Number of blocks ("lines"). Has to be a power of two. |

|

boolean |

false |

Implement the data cache ("D$") |

|

natural |

4 |

Number of blocks ("lines"). Has to be a power of two. |

|

natural |

64 |

global cache block size (I$ and D$) in bytes. Has to be a power of two, min 4. |

|

boolean |

true |

Enable burst transfers for cache updates. |

Processor-External Bus Interface (XBUS) (Wishbone / AXI4-Compatible Bridging) |

|||

|

boolean |

false |

Implement the external bus interface. |

|

natural |

2048 |

Number of clock cycles after which an unacknowledged external bus access will auto-terminate (0 = disabled). |

|

boolean |

false |

Implement XBUS register stages to ease timing closure. |

|

natural |

0 |

Number of GPIO pairs, max 32. |

|

boolean |

false |

Enable optional GPIO direction control interface ( |

|

boolean |

false |

Implement CLINT. |

Primary Universal Asynchronous Receiver and Transmitter (UART0) |

|||

|

boolean |

false |

Implement UART0. |

|

natural |

1 |

UART0 RX FIFO depth, has to be a power of two, minimum value is 1, max 32768. |

|

natural |

1 |

UART0 TX FIFO depth, has to be a power of two, minimum value is 1, max 32768. |

Secondary Universal Asynchronous Receiver and Transmitter (UART1) |

|||

|

boolean |

false |

Implement UART1. |

|

natural |

1 |

UART1 RX FIFO depth, has to be a power of two, minimum value is 1, max 32768. |

|

natural |

1 |

UART1 TX FIFO depth, has to be a power of two, minimum value is 1, max 32768. |

|

boolean |

false |

Implement SPI controller. |

|

natural |

1 |

Depth of the SPI FIFO. Has to be a power of two, min 1, max 32768. |

|

boolean |

false |

Implement SDI controller. |

|

natural |

1 |

Depth of the SDI FIFO. Has to be a power of two, min 1, max 32768. |

|

boolean |

false |

Implement TWI controller. |

|

natural |

1 |

Depth of the TWI FIFO. Has to be a power of two, min 1, max 32768. |

|

boolean |

false |

Implement TWD controller. |

|

natural |

1 |

Depth of the TWD RX FIFO. Has to be a power of two, min 1, max 32768. |

|

natural |

1 |

Depth of the TWD TX FIFO. Has to be a power of two, min 1, max 32768. |

|

natural |

0 |

Number of PWM channels to implement (0..32). |

|

boolean |

false |

Implement WDT. |

|

boolean |

false |

Implement TRNG. |

|

natural |

1 |

Depth of the TRNG data FIFO. Has to be a power of two, min 1, max 32768. |

|

natural |

3 |

Total number of ring-oscillators. |

|

natural |

5 |

Number of inverters in first ring-oscillator; has to be odd. |

|

natural |

64 |

Number of raw random bits to process for one output byte; has to be power of 2. |

|

boolean |

false |

Implement CFS. |

|

boolean |

false |

Implement NEOLED controller. |

|

natural |

1 |

TX FIFO depth of the NEOLED controller. Has to be a power of two, min 1, max 32768. |

|

natural |

0 |

Number of individual GPTMR timer slices (0..16). |

|

boolean |

false |

Implement 1-wire controller. |

|

natural |

1 |

Depth of the 1-Wire FIFO. Has to be a power of two, min 1, max 32768. |

|

boolean |

false |

Implement DMA controller. |

|

natural |

4 |

Depth of the DMA transfer descriptor FIFO. Has to be a power of two, min 4, max 512. |

|

boolean |

false |

Implement stream link interface (AXI4-Stream-Compatible). |

|

natural |

1 |

SLINK RX FIFO depth, has to be a power of two, minimum value is 1, max 32768. |

|

natural |

1 |

SLINK TX FIFO depth, has to be a power of two, minimum value is 1, max 32768. |

|

boolean |

false |

Implement the trace buffer. |

|

natural |

1 |

Depth of the trace buffer. Has to be a power of two, min 1, max 32768. |

|

boolean |

false |

Write full trace log to file (simulation-only). |

2.3. Processor Clocking

The entire system is implemented as fully-synchronous logic design using a single clock domain that is driven

by the top’s clk_i signal. This clock signal is used by all internal registers and memories. All of them trigger

on the rising edge of this clock signal. External "clocks" like the OCD’s JTAG clock or the SDI’s serial clock

are synchronized into the processor’s clock domain before being used as "general logic signal" (and not as a dedicated clock).

2.3.1. Peripheral Clocks

Many processor modules like the UARTs or the timers provide a programmable time base for operations. In order to simplify

the hardware, the processor implements a global "clock generator" (neorv32_sys.vhd) that provides single-cycle clock enables

for certain frequencies which are derived from the main clock. These clock enable signals are synchronous to the system’s

main clock. The processor modules can use these enables for sub-main-clock operations while still providing a single

clock domain only.

In total, 8 sub-main-clock signals are available. All processor modules, which feature a time-based configuration, provide a

programmable three-bit prescaler select in their control register to select one of the 8 available clocks. The

mapping of the prescaler select bits to the according clock source is shown in the table below. Here, f represents the

processor main clock from the top entity’s clk_i signal.

Prescaler bits: |

|

|

|

|

|

|

|

|

Resulting clock: |

f/2 |

f/4 |

f/8 |

f/64 |

f/128 |

f/1024 |

f/2048 |

f/4096 |

2.4. Processor Reset

The NEORV32 processor includes a central reset sequencer (neorv32_sys.vhd) that handles all reset requests

and controls the internal reset nets. The processor-wide reset ("system reset") can be triggered by any

of the following sources:

-

the asynchronous low-active

rstn_itop entity input signal (external source) -

the On-Chip Debugger (OCD) (internal source)

-

the Watchdog Timer (WDT) (internal source)

|

Reset Cause

The actual reset cause can be determined via the Watchdog Timer (WDT).

|

If any of these sources triggers a reset, the internal system-wide reset will be active for at least 4 clock cycles ensuring

a valid reset of the entire processor. This system reset is asserted asynchronoulsy if triggered by the external

rstn_i signal and is asserted synchronously if triggered by an internal reset source. However, the system reset is

always de-asserted synchronously at the next rising clock edge.

Internally, all registers that are not meant for mapping to blockRAM (like the register file) do provide a dedicated and low-active asynchronous hardware reset. This asynchronous reset ensures that the entire processor logic is reset to a defined state even if the main clock is not operational yet.

2.5. Processor Interrupts

The system offers several interrupts (IRQs). Some can be used freely, others are reserved for specific tasks.

|

Trigger Type

All interrupt request lines are level-triggered and high-active. Once set, the signal should remain high until

the interrupt request is explicitly acknowledged (e.g. by writing to a memory-mapped register).

|

2.5.1. RISC-V Standard Interrupts

The processor supports the standard RISC-V machine-level interrupts for "machine timer interrupt (MTI)", "machine software interrupt (MSI)" and "machine external interrupt (MEI)". Their usage is defined by the RISC-V privileged architecture specification. See CPU section Traps, Exceptions and Interrupts for more information.

| Top signal | Description |

|---|---|

|

Machine software interrupt ( |

|

Machine timer interrupt ( |

|

Machine external interrupt ( |

2.5.2. NEORV32-Specific Fast Interrupt Requests

As part of the NEORV32-specific CPU extensions, the processor core features 16 fast interrupt request signals

(FIRQ0 to FIRQ15) with dedicated bits in mip and mie CSRs and custom mcause trap codes.

The FIRQ signals are reserved for processor-internal modules only (for example for the communication

interfaces to signal "available incoming data" or "ready to send new data").

The mapping of the 16 FIRQ channels to the according processor-internal modules is shown in the following table. The channel number also corresponds to the according FIRQ priority (0 = highest, 15 = lowest):

| Channel (priority) | Source |

|---|---|

0 |

reserved |

1 |

|

2 |

Primary Universal Asynchronous Receiver and Transmitter (UART0) |

3 |

Secondary Universal Asynchronous Receiver and Transmitter (UART1) |

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

12 |

|

13 |

|

14 |

|

15 |

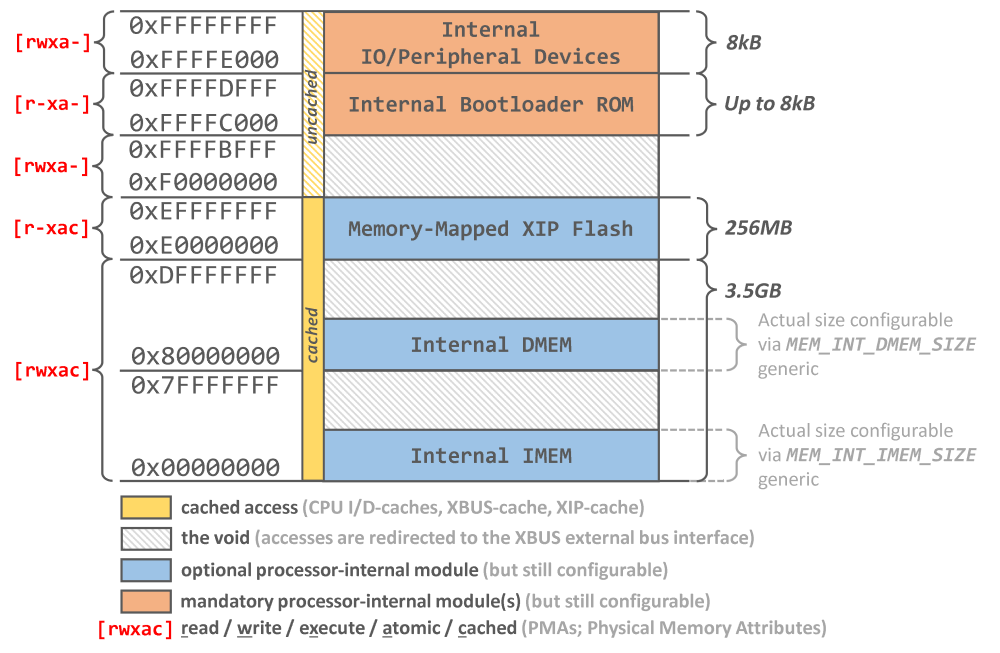

2.6. Address Space

As a 32-bit architecture, NEORV32 can access 4GB of physical address space. This address space is divided into two

regions: the lower 3.75 GB (0x00000000 … 0xEFFFFFFF) are referred to as Memory Address Space while

the upper 256 MB (0xF0000000 … 0xFFFFFFFF) are referred to as IO/Peripheral Address Space.

The memory address space is intended for actual memory and provides fully cached accesses from the instruction and data caches of the CPU(s). In contrast, the IO/peripheral address space is dedicated for memory-mapped IO and provides direct / uncached accesses only. Note that the address ranges for cached and uncached accesses are hard-wired and are not intended to be customized by the user.

How these two address regions are used is ultimately up to the user. However, in the default processor configuration

the memory address space can be optionally populated with processor-internal instruction and data memories. By default,

the processor-internal Instruction Memory (IMEM) is mapped to base address 0x00000000 and the processor- internal

Data Memory (DMEM) is mapped to base address 0x80000000. The very last 2 MB of the IO/peripheral address space is

exclusively reserved for the NEORV32-internal memory-mapped IO and peripheral modules.

Accesses to "unmapped" addresses (a.k.a. the void) are redirected to the Processor-External Bus Interface (XBUS).

For example, if the processor-internal IMEM is disabled, accesses to the addresses starting at 0x00000000 are also

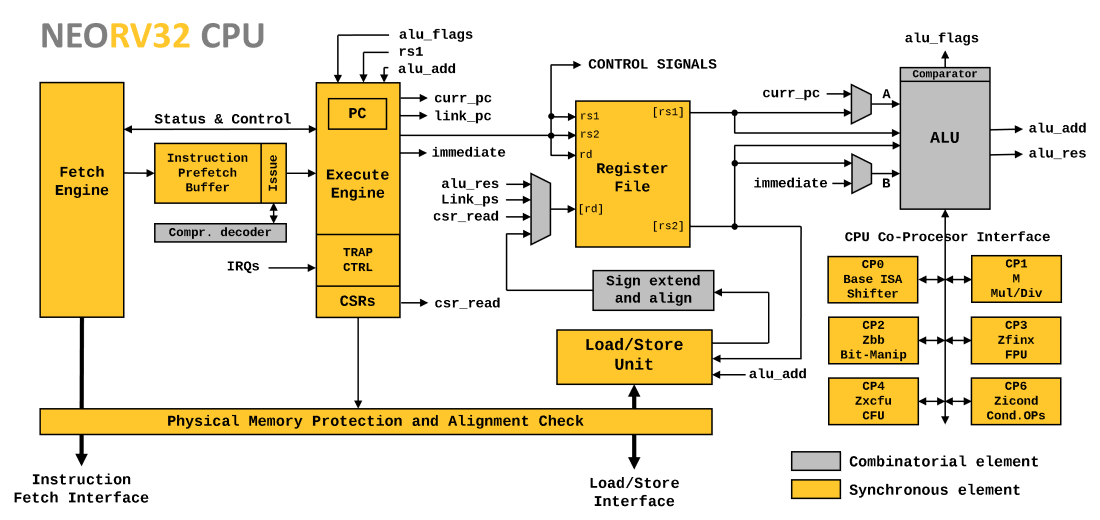

redirected to the external bus interface. If the external bus interface is not enabled any access to the void will raise

a bus error exception.

|

Physical Memory Attributes "PMAs"

The address space regions provides specific physical memory attributes that define the access capabilities:

r = read access, w = write access, x = execute access, a = atomic access, c = cached CPU access.

Custom physical memory attributes enforced by the CPU’s physical memory protection "PMP" (Smpmp ISA Extension)

can be used to further constrain the physical memory attributes.

|

2.6.1. Bus System

The CPU core provides individual interfaces for instruction fetch and data access. Both interface access the same address space making the core a von-Neumann architecture. Optionally, the two interface can be equipped with data and/or instruction caches (i-cache & d-cache).

The two CPU interfaces are multiplexed by a simple bus switch into a single processor-internal bus. Optionally, this bus is further multiplexed by another instance of the bus switch so the Direct Memory Access Controller (DMA) can also access the entire address space.

Accesses via the resulting SoC bus are routed by the Bus Gateway that is used to redirect the access to the processor-internal Instruction Memory (IMEM) (if implemented), the processor-internal Data Memory (DMEM) (if implemented), the processor-internal peripheral devices or - if the access does not target any of these - the Processor-External Bus Interface (XBUS). Accesses to the processor-internal IO/peripheral devices are further redirected via a dedicated IO Switch.

|

Bus System Infrastructure IP

The individual components of the processor’s bus system infrastructure are defined in rtl/core/neorv32_bus.vhd.

|

|

Bus Interface

See sections CPU Architecture and Bus Interface for more information regarding the CPU bus accesses

and the according protocol.

|

|

SMP Dual-Core Configuration

The dual-core configuration adds a second CPU core complex in parallel to the first one.

See section Dual-Core Configuration for more information.

|

2.6.2. Bus Gateway

The central bus gateway (VHDL component neorv32_bus_gateway) distributes CPU accesses to the two main memory

regions. Depending on the configuration, it routes accesses to:

-

Instruction Memory (IMEM) (if implemented)

-

Data Memory (DMEM) (if implemented)

-

processor-internal IO/peripherals

-

Processor-External Bus Interface (XBUS) (if implemented)

Additionally, the gateway also provides a bus monitor (aka "the bus keeper") that tracks all bus transactions to ensure safe and deterministic operations.

Bus Monitor and Timeout

For each single access the bus monitor starts an internal countdown.

The accessed module has to respond to the bus request within a bound time window. For processor-internal accesses

this time windows is defined by a constant in the main NEORV32 package file. For processor-external accesses

(via the external bus interface) this timeout is defined by the XBUS_TIMEOUT top configuration generic.

neorv32_package.vhd)constant int_bus_tmo_c : natural := 16; -- internal bus timeout window; has to be a power of twoneorv32_top.vhd)XBUS_TIMEOUT : natural := 2048; -- cycles after a pending bus access auto-terminates (0 = disabled)The according time window defines the maximum number of cycles after which a non-responding bus request will time out raising a bus access fault exception. For example this can happen when accessing "address space holes" - addresses that are not mapped to any physical module at all. The specific bus access exception type corresponds to the according access type (i.e. instruction fetch bus access fault, load bus access fault or store bus access fault).

2.6.3. IO Switch

The IO switch (VHDL component neorv32_bus_io_switch) decodes accesses to the procesor-internal IO/peripheral

address space. This 2MB address space is used to map all NEORV32 peripherals (like UART, SPI, timers, etc.),

the bootloader ROM and the on-chip debugger. Each device occupies an address range of 64kB; so up to 32 individual

devices can be mapped. The according address map is defined in the main VHDL package file (rtl/core/neorv32_package.vhd).

2.6.4. Atomic Memory Operations Controller

The CPU’s A ISA Extension adds support for atomic memory accesses. These atomic memory accesses are handles by

dedicated modules of the processor bus system. The SoC bus that is driven by the CPU core(s) is fed through two

atomic memory controller modules that handle read-modify-write operations as well as reservation-set operation:

| Hardware Module | CPU ISA Extensions | Description |

|---|---|---|

|

||

|

|

Direct/Non-Caches Atomic Accesses

Atomic operations always bypass the CPU’s data cache

using direct/uncached accesses. Care must be taken to maintain data Memory Coherence.

|

|

Physical Memory Attributes

Atomic memory operations can be executed targeting any address. This also includes

cached memory, memory-mapped IO devices and processor-external address spaces.

|

Atomic Read-Modify-Write Controller

This modules converts a single read-modify-write (RMW) memory operations request into two consecutive and atomic bus transactions. For each request, the controller executes an atomic set of three operations:

| Step | Pseudo Code | Description |

|---|---|---|

1 |

|

Perform a read operation from the targeted memory

address and temporarily store the loaded data into an internal buffer ( |

2 |

|

The buffered data from the first step is processed

using the write data provided by the CPU. The result is stored to another temporary internal buffer ( |

3 |

|

The data from the second buffer ( |

Atomic Reservation-Set Controller

In NEORV32 a reservation is defined by a 64-byte address granule that provides a guarding mechanism to support

atomic accesses (as specified by the RISC-V Zalrsc ISA Extension). A new reservation is registered by the

LR instruction. The address provided by this instruction defines the 64-byte-aligned memory region that is

monitored for exclusive accesses. The according SC instruction evaluates the state of this reservation. If the

reservation is still valid (same owner core / issueing core and same address granule) the write access performed by

the SC instruction is finally executed and the instruction returns a success state (i.e. rd = 0). If the

reservation has been invalidated or does not match, the SC instruction will not update main memory and will return

a failed state (i.e. rd = 1).

In either case, the SC instruction issues a downstream bus access to main memory (converted to a READ in case

of failure) to allow the detection of access faults for the target address also for failed SC instructions

which is required by the RISC-V specs.

|

The reservation-set controller implements a single reservation set per instance with a fixed granularity of 64 bytes.

Each reservation tracks the owning core’s ID and the aligned base address. A reservation is invalidated only when a

write access targets the same 64-byte address granule - read accesses, instruction fetches, and fence[.i] instructions

do not affect the reservation state.

The reservation-set controller is shared by both cores in the SMP Dual-Core Configuration. To ensure forward progress during concurrent atomic sequences, a turn-based arbitration mechanism is implemented:

-

An

LRinstruction can create (or update) a reservation if no reservation is active, if the requesting core already owns the current reservation, or if it is the requesting core’s "turn" (priority). -

A successful

SCflips the turn, ensuring that the other core receives priority for its nextLRattempt. -

A failed

SCfrom the owning core also clears the reservation, preventing stale reservations from blocking progress.

This guarantees atomic accesses and mutually exclusive access without starvation.

|

External Reservations

Note that the reservation-set controller cannot track memory accesses outside of the NEORV32 processor

(i.e. atomic accesses via the external bus interface) that are executed by processor-external agents.

|

2.6.5. Memory Coherence

Depending on the configuration, the NEORV32 memory hierarchy provides several levels/layers of memory.

-

The CPU execution pipeline and its instruction prefetch buffer (CPU Front-End)

-

The optional Data Cache (dCache) and Instruction Cache (iCache)

-

Processor-internal and processor-external memories (depending on setup configuration)

NEORV32 can feature up to three bus hosts: up to two CPU cores and the Direct Memory Access Controller (DMA). Since the levels of the memory hierarchy are transparent to the software, special care must be taken to ensure memory coherence is maintained throughout the entire system/application. Note that coherence and especially cache synchronization is not performed automatically by the hardware itself as there is no snooping implemented. NEORV32 supports two RISC-V memory ordering instructions that are used for manual memory synchronization:

-

fence(IISA Extension /EISA Extension): Flush the CPU’s data cache: Modified ("dirty") blocks are copied back to main memory; all clean blocks are invalidated so that the next CPU access to any block results in a cache miss that reloads the cache with up-to-date data from main memory. -

fence.i(ZifenceiISA Extension): Perform the same operations asfence(i.e. flushing the data cache), but also clear the CPU’s instruction prefetch buffer and instruction cache. The next instruction cache access therefore results in a miss that fetches up-to-date data from main memory.

|

Weak Coherence Model

The NEORV32-specific implementation of the fence[.i] ordering instructions only provides a rather weak

coherence model. A core’s fence just orders all memory accesses towards main memory. Hence, they can become

visible by other agents (the secondary CPU core, the DMA, processor-external modules) if these agents also

synchronize (e.g. reload) their cache(s).

|

Atomic memory accesses also require special attention. All atomic memory accesses bypass the CPU caches. However, in this case, the caches explicitly ensure memory coherence. If the address of an atomic memory access is cached, the corresponding line is first written back to main memory if it has been modified. Afterward, the corresponding line is invalidated, and the atomic access is executed as a cache bypass. The next access to the atomic address bypasses the cache if it is again an atomic memory operation. Normal memory accesses result in a cache miss (since the corresponding line was automatically invalidated previously), so that the cache is reloaded with current data from main memory.

|

C-Language

Using plain _Atomic VariablesAtomic access (e.g., _Atomic int counter = 0;) defaults to GCC’s memory_order_seq_cst

buildin, which inserts fence instructions _before and after the access. This is the safest but slowest option.

|

2.7. Boot Configuration

The NEORV32 processor provides pre-defined boot configurations to adjust system start-up to

the requirements of the application. The actual boot configuration is defined by the BOOT_MODE_SELECT

generic (see Processor Top Entity - Generics).

For the SMP dual-core CPU configuration boot procedure see section Dual-Core Boot.

BOOT_MODE_SELECT |

Name | Boot address | Description |

|---|---|---|---|

0 (default) |

Bootloader |

Base of internal BOOTROM |

Implement the processor-internal Bootloader ROM (BOOTROM) as pre-initialized ROM and boot from there. |

1 |

Custom Address |

|

Start booting at user-defined address ( |

2 |

IMEM Image |

Base of internal IMEM |

Implement the processor-internal Instruction Memory (IMEM) as pre-initialized ROM and boot from there. |

2.7.1. Booting via Bootloader

This is the default configuration. When selected, the processor-internal Bootloader ROM (BOOTROM) is enabled.

This ROM contains the executable image (rtl/core/neorv32_bootrom_image.vhd) of the default NEORV32 Bootloader

that will be executed right after reset. The bootloader provides an interactive user console for executable upload as

well as an automatic mode to boot from external (SPI) flash memory.

If the processor-internal Instruction Memory (IMEM) is enabled it will be implemented as blank RAM.

2.7.2. Boot from Custom Address

This is the most flexible boot configuration as it allows the user to specify a custom boot address via the

BOOT_ADDR_CUSTOM generic. Note that this address has to be aligned to 4-byte boundary. The processor will

start executing from the defined address right after reset. For example, this boot configuration ca be used to

execute a custom bootloader from a memory that is attached via the Processor-External Bus Interface (XBUS).

For this configuration the processor-internal Bootloader ROM (BOOTROM) is not enabled / implement at all. If the processor-internal Instruction Memory (IMEM) is enabled it will be implemented as blank RAM.

2.7.3. Boot IMEM Image

This configuration will implement the Instruction Memory (IMEM) as pre-initialized ROM. The ROM is

initialized during synthesis with the according application image file (rtl/core/neorv32_imem_image.vhd).

After reset, the CPU will directly start executing this image. Since the IMEM is implemented as ROM, the

executable cannot be altered at runtime at all.

For this configuration the Bootloader ROM (BOOTROM) is not enabled / implement at all.

Note that this boot configuration requires the IMEM to be enabled (IMEM_EN = true).

|

Simulation Setup

This boot configuration is handy for simulations as the application software is executed right away without the

need for an explicit initialization / executable upload.

|

2.8. Processor-Internal Modules

|

Full-Word Write Accesses Only

Unless otherwise specified, all peripheral/IO devices should only be accessed using full-word accesses (i.e. 32-bit).

|

|

IO Module Address Space

Each peripheral/IO module occupies an address space of 64kB bytes. Most devices do not fully utilize this

address space and will mirror the available memory-mapped registers across the device’s address space.

However, only the specified memory-mapped registers addresses should be used.

|

|

Unimplemented Modules / Address Holes

When accessing an IO device tha hast not been implemented (disabled via the according generic)

or when accessing an address that is actually unused, a load/store access fault exception is raised.

|

|

Writing to Read-Only Registers

Unless otherwise specified, writing to registers that are listed as read-only does not trigger an exception

as the write access is just ignored by the corresponding hardware module.

|

|

Module Interrupts

Several peripheral/IO devices provide some kind of interrupt. These interrupts are mapped to the CPU’s

Custom Fast Interrupt Request Lines. See section Processor Interrupts for more information.

|

|

CMSIS System Description View (SVD)

A CMSIS-compatible System View Description (SVD) file including all peripherals is available in sw/svd.

|

2.8.1. Instruction Memory (IMEM)

Hardware source files: |

neorv32_imem.vhd |

generic processor-internal instruction memory (RAM or ROM) |

neorv32_imem_image.vhd |

memory initialization image (VHDL package) |

|

neorv32_imem_ram.vhd |

RAM component (primitive/IP wrapper) |

|

neorv32_imem_rom.vhd |

ROM component (primitive/IP wrapper) |

|

Software driver files: |

none |

|

Top entity ports: |

none |

|

Configuration generics: |

|

implement IMEM when |

|

32-bit base address (naturally aligned to IMEM size) |

|

|

IMEM size in bytes (use a power of 2) |

|

|

add IMEM output register stage |

|

|

implement IMEM as ROM when |

|

CPU interrupts: |

none |

Key Features

-

Burst-capable tightly-coupled on-chip instruction memory

-

Configurable RAM size

-

Accessible at the byte level

-

Mapped to memory primitives

-

Optional output register for improved timing

-

Can be implemented as pre-initialized ROM containing application firmware

Overview

Implementation of the processor-internal instruction memory is enabled by the processor’s

IMEM_EN generic. The total memory size in bytes is defined via the IMEM_SIZE generic.

Only sizes that are powers of two are supported. If enabled, the IMEM is mapped to base

address 0x00000000 by default (see section Address Space).

|

Custom IMEM Base Address

The base address of the IMEM can be customized via the IMEM_BASE generic. Please note that

the selected address must be naturally aligned to the IMEM size (IMEM_SIZE) and that there must

be no overlap with other sections of the internal Address Space (internal DMEM if enabled

and the internal IO/peripheral address space). Any non-default address must also be passed to the

Linker Script (e.g. USER_FLAGS += -Wl,--defsym,__neorv32_rom_base=<IMEM_BASE>).

|

By default the IMEM is implemented as true RAM so the content can be modified during run time.

Alternatively, the IMEM can be implemented as pre-initialized read-only memory (ROM), so the

processor can directly boot from it after reset. This option is configured via the BOOT_MODE_SELECT

generic. See section Boot Configuration for more information. If the IMEM is implemented as ROM

any write attempt to it will raise a store access fault exception.

The software framework provides an option to generate and override the default VHDL initialization

file rtl/core/neorv32_imem_image.vhd, which is automatically inserted into the IMEM (see

Makefile Targets. If the IMEM is implemented as RAM (default), the memory block will not be

initialized at all.

|

Output Register Stage

An optional output register stage can be enabled via IMEM_OUTREG_EN. For FPGA targets this might improve

mapping/timing results. Note that this option will increase the read latency by one clock cycle. Write accesses

are not affected by this at all.

|

|

Retrieve Memory Configuration by Software

Software can retrieve the DMEM size from the SYSINFO - Miscellaneous Configuration register.

|

|

Memory Primitives

The memory’s memory core is encapsulated as individual wrapper (neorv32_imem_ram.vhd / neorv32_imem_ram.vhd)

that can be replaced by a technology-specific IP. All interface ports provide static signal widths to ease replacement.

|

2.8.2. Data Memory (DMEM)

Hardware source files: |

neorv32_dmem.vhd |

generic processor-internal data memory (RAM) |

neorv32_dmem_ram.vhd |

RAM component (primitive/IP wrapper) |

|

Software driver files: |

none |

|

Top entity ports: |

none |

|

Configuration generics: |

|

implement DMEM when |

|

32-bit base address (naturally aligned to DMEM size) |

|

|

DMEM size in bytes (use a power of 2) |

|

|

add DMEM output register stage |

|

CPU interrupts: |

none |

Key Features

-

Burst-capable tightly-coupled on-chip data memory

-

Configurable RAM size

-

Accessible at the byte level

-

Can also be used for executing code

-

Mapped to memory primitives

-

Optional output register for improved timing

Overview

Implementation of the processor-internal data memory is enabled by the processor’s DMEM_EN

generic. The total memory size in bytes is defined via the DMEM_SIZE generic. Only sizes that

are powers of two are supported. If enabled, the DMEM is mapped to base address 0x80000000

by default (see section Address Space).

|

Custom DMEM Base Address

The base address of the DMEM can be customized via the DMEM_BASE generic. Please note that

the selected address must be naturally aligned to the DMEM size (DMEM_SIZE) and that there must

be no overlap with other sections of the internal Address Space (internal IMEM if enabled

and the internal IO/peripheral address space). Any non-default address must also be passed to the

Linker Script (e.g. USER_FLAGS += -Wl,--defsym,__neorv32_ram_base=<DMEM_BASE>).

|

|

Platform-Specific Memory Primitives

If required, the default DMEM can be replaced by a platform-/technology-specific primitive to

optimize area utilization, timing and power consumption.

|

|

Output Register Stage

An optional output register stage can be enabled via DMEM_OUTREG_EN. For FPGA targets this might improve

mapping/timing results. Note that this option will increase the read latency by one clock cycle. Write accesses

are not affected by this at all.

|

|

Retrieve Memory Configuration by Software

Software can retrieve the DMEM size from the SYSINFO - Miscellaneous Configuration register.

|

|

Memory Primitives

The memory’s memory core is encapsulated as individual wrapper (neorv32_dmem_ram.vhd) that can be

replaced by a technology-specific IP. All interface ports provide static signal widths to ease replacement.

|

2.8.3. Bootloader ROM (BOOTROM)

Hardware source files: |

neorv32_bootrom.vhd |

default platform-agnostic bootloader ROM |

neorv32_bootrom_image.vhd |

memory initialization image |

|

neorv32_bootrom_rom.vhd |

ROM component (primitive/IP wrapper) |

|

Software driver files: |

none |

implicitly used |

Top entity ports: |

none |

|

Configuration generics: |

|

implement BOOTROM when |

CPU interrupts: |

none |

Key Features

-

Tightly-coupled on-chip ROM

-

Accessible at the byte level

-

Mapped to memory primitives

-

Pre-initialized with default NEORV32 bootloader

Overview

The boot ROM contains the pre-compiled executable image of the default NEORV32 Bootloader. When the

Boot Configuration is set to bootloader mode (0) via the BOOT_MODE_SELECT generic, the

boot ROM is automatically enabled and the CPU boot address is adjusted to the base address of the boot ROM.

Note that the entire boot ROM is read-only.

|

Bootloader Image

The bootloader ROM is initialized during synthesis with the default bootloader image

(rtl/core/neorv32_bootrom_image.vhd). The physical size of the ROM is automatically

adjusted to the next power of two of the image size. However, note that the BOOTROM is

constrained to a maximum size of 64kB.

|

|

Memory Primitives

The memory’s memory core is encapsulated as individual wrapper (neorv32_bootrom_rom.vhd)

that can be replaced by a technology-specific IP. All interface ports provide static signal

widths to ease replacement.

|

2.8.4. Instruction Cache (iCache)

Hardware source files: |

neorv32_cache.vhd |

generic cache module |

neorv32_cache_ram.vhd |

tag and data RAM (primitive/IP wrapper) |

|

Software driver files: |

none |

|

Top entity ports: |

none |

|

Configuration generics: |

|

implement CPU-exclusive instruction cache (I$) when |

|

number of cache blocks ("cache lines"); has to be a power of two |

|

|

size of a cache block in bytes (global configuration for I$ and D$); has to be a power of two, min 4 |

|

|

enable burst transfers for cache update |

|

CPU interrupts: |

none |

Key Features

-

Direct-mapped read-only cache

-

Configurable number of lines

-

Configurable line size

-

Allows bypassing for uncached accesses

-

Tag and data RAM mapped to memory primitives

Overview

The processor features an optional instruction cache (i-cache) that is directly connected to the CPU Front-End instruction fetch interface providing full-transparent accesses. The cache is direct-mapped and read-only. For the Dual-Core Configuration each CPU core is equipped with a private instruction cache.

The instruction cache is enabled by the ICACHE_EN generic. The total cache memory size in bytes is defined

by ICACHE_NUM_BLOCKS x CACHE_BLOCK_SIZE. ICACHE_NUM_BLOCKS defines the number of cache blocks ("lines")

and CACHE_BLOCK_SIZE defines the block (line) size in bytes; note that the latter configuration is global

for all caches.

|

Retrieve Cache Configuration by Software

Software can retrieve the cache configuration/layout from the SYSINFO - Cache Configuration register.

|

|

Memory Primitives

The cache’s tag and data RAMs are encapsulated as wrapper (neorv32_cache_ram.vhd) that can be modified or

replaced by a technology-specific IP. All interface ports provide static signal widths to ease replacement.

|

Burst Transfers

Cache update operations can use burst transfers to increase performance.

Burst operations are enabled (for all caches) by the CACHE_BURSTS_EN top generic. When bursts are enabled

all cache block transfers are always executed as burst transfers. Hence, all devices, memories and endpoints

that can be accessed by the cache must also be able to process bursts (including modules connected to the

Processor-External Bus Interface (XBUS)).

Cache Bypass

The cache provides direct/uncached accesses (bypassing the cache) in order to access memory-mapped IO like

the processor-internal IO/peripheral modules. All accesses that target the address range from 0xF0000000

to 0xFFFFFFFF will bypass the cache. See section Address Space for more information.

All atomic memory accesses also bypass the cache; however, in this case, the cache explicitly ensures Memory Coherence: if the address of an atomic memory access is cached, the corresponding line is first written back to main memory if it has been modified. The corresponding line is then invalidated, and the atomic access is finally executed as a cache-bypassing access.

Cache Synchronization and Memory Coherence

By executing the fence.i instruction the entire i-cache is invalidated. The next access therefore results

in a cache miss that reloads the cache with up-to-date data from main memory. See section

Memory Coherence for more information.

Cache Bus Error Handling

The cache responds differently to bus errors depending on which operation caused the error. Note that all instruction cache accesses are entirely read-only.

-

Cache Bypass: If a bus error occurs during a cache bypass operation - for example, when accessing memory-mapped I/O - the bus error is reported to the CPU immediately and with full precision. The address reported in

mepcrepresents the exact address that caused the error. -

Cache Miss: If the instruction request results in a cache miss, the according memory block is fetched from main memory. If any memory access within this block transfer causes a bus error, the entire cache block is discarded and the bus error is reported to the CPU immediately and with partial precision. The address reported in

mepcrepresents an address within the cache/memory block whose fetch caused the error. -

Cache Synchronization: A cache synchronization operation (

fence.i) cannot cause any bus error as it just invalided all current cache blocks without performing any memory access at all.

2.8.5. Data Cache (dCache)

Hardware source files: |

neorv32_cache.vhd |

generic cache module |

neorv32_cache_ram.vhd |

tag and data RAM (primitive/IP wrapper) |

|

Software driver files: |

none |

|

Top entity ports: |

none |

|

Configuration generics: |

|

implement CPU-exclusive data cache (D$) when |

|

number of cache blocks ("cache lines"); has to be a power of two |

|

|

size of a cache block in bytes (global configuration for I$ and D$); has to be a power of two, min 4 |

|

|

enable burst transfers for cache update |

|

CPU interrupts: |

none |

Key Features

-

Direct-mapped cache with write-back & write-allocated write policies

-

Configurable number of lines

-

Configurable line size

-

Allows bypassing for uncached accesses

-

Tag and data RAM mapped to memory primitives

Overview

The processor features an optional data cache (d-cache) that is directly connected to the CPU Load/Store Unit data interface providing full-transparent accesses. The cache is direct-mapped and uses write-back (copy modified cache lines back to main memory when evicted) and write-allocate (fetch entire line on a write-miss) write policies. For the Dual-Core Configuration each CPU core is equipped with a private data cache.

The data cache is enabled by the DCACHE_EN generic. The total cache memory size in bytes is defined by

DCACHE_NUM_BLOCKS x CACHE_BLOCK_SIZE. DCACHE_NUM_BLOCKS defines the number of cache blocks ("lines")

and CACHE_BLOCK_SIZE defines the block (line) size in bytes; note that the latter configuration is global

for all caches.

|

Retrieve Cache Configuration by Software

Software can retrieve the cache configuration/layout from the SYSINFO - Cache Configuration register.

|

|

Memory Primitives

The cache’s tag and data RAM is encapsulated as individual wrapper (neorv32_cache_ram.vhd) that can be

replaced by a technology-specific IP. All interface ports provide static signal widths to ease replacement.

|

Burst Transfers

Cache update operations can use burst transfers to increase performance.

Burst operations are enabled (for all caches) by the CACHE_BURSTS_EN top generic. When bursts are enabled

all cache block transfers are always executed as burst transfers. Hence, all devices, memories and endpoints

that can be accessed by the cache must also be able to process bursts (including modules connected to the

Processor-External Bus Interface (XBUS)).

Cache Bypass

The cache provides direct/uncached accesses (bypassing the cache) in order to access memory-mapped IO like

the processor-internal IO/peripheral modules. All accesses that target the address range from 0xF0000000

to 0xFFFFFFFF will bypass the cache. See section Address Space for more information.

All atomic memory accesses also bypass the cache; however, in this case, the cache explicitly ensures Memory Coherence: if the address of an atomic memory access is cached, the corresponding line is first written back to main memory if it has been modified. The corresponding line is then invalidated, and the atomic access is finally executed as a cache-bypassing access.

Cache Synchronization and Memory Coherence

By executing the fence instruction the data cache is flushed: modified ("dirty") blocks are copied back to main

memory; all clean blocks are invalidated so that the next CPU access to any block results in a cache miss that

reloads the cache with up-to-date data from main memory. See section Memory Coherence for more information.

Cache Bus Error Handling

The cache responds differently to bus errors depending on which operation caused the error.

-

Cache Bypass: If a bus error occurs during a cache bypass operation - for example, when accessing memory-mapped I/O - the bus error is reported to the CPU immediately and with full precision. The address reported in

mtvalrepresents the exact address that caused the error. -

Cache Miss Without Eviction: If the CPU request results in a cache miss that can be completed without, the according memory block is fetched from main memory. If any memory access within this block transfer causes a bus error, the entire cache block is discarded and the bus error is reported to the CPU immediately and with partial precision. The address reported in

mtvalrepresents an address within the cache/memory block whose fetch caused the error. -

Cache Miss With Eviction: If the CPU request results in a cache miss that requires the write-back of a modified ("dirty") cache block, the modified is copied back to main memory before fetching the actual requested memory block. If this write-back causes any buss error, the modified cache block being written back is discarded and the bus error is reported to the CPU immediately and imprecisley. The address reported in

mtvalonly represents an address inside the requested memory block - not an address within the block that the cache was trying to write back.

|

Bus-Errors During Cache Write-Back

This type of cache-related "background" bus error is difficult to debug and - like most other bus errors - might

be fatal when occurring in machine mode. A future version of NEORV32 will include an improved mechanism for

determining the exact address of this type of bus error.

|

-

Cache Synchronization: If the cache encounters a bus error while writing modified cache blocks back to main memory during a cache synchronization operation (